|   | SKIT      | Teaching Process  | Rev No.: 1.0    |

|---|-----------|-------------------|-----------------|

| ) | Doc Code: | EC.SKIT.Ph5b1.F03 | Date:18-10-2019 |

|   | Title:    | Course Lab Manual | Page: 1 / 71    |

# Table of Contents

| 18ECL38 : DIGITAL SYSTEM DESIGN LAB          | )        |

|----------------------------------------------|----------|

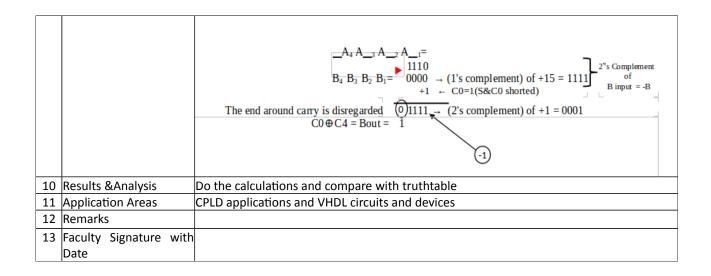

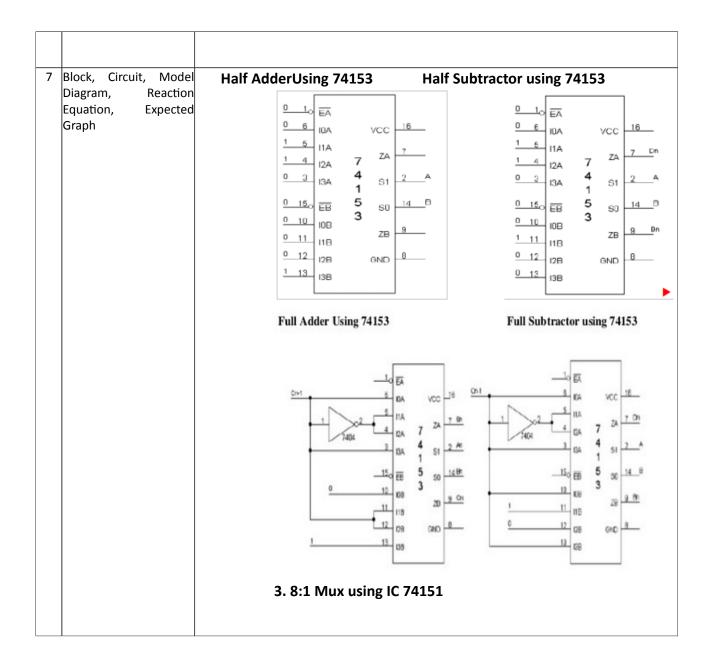

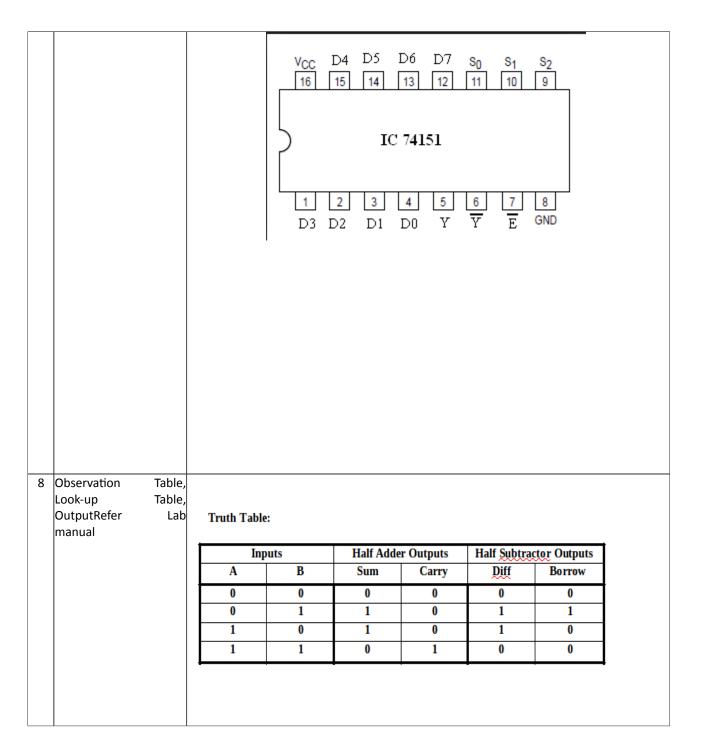

| A. LABORATORY INFORMATION                    | )        |

| <u>1. Lab Overview</u> <u>2</u>              | )        |

| <u>2. Lab Content</u>                        | )        |

| <u>3. Lab Material</u> <u>2</u>              | )        |

| <u>4. Lab Prerequisites:</u> <u>3</u>        | }        |

| 5. General Instructions                      | }        |

| <u>6. Lab Specific Instructions</u> <u>3</u> | }        |

| B. OBE PARAMETERS                            | }        |

| <u>1. Lab / Course Outcomes</u> <u>3</u>     | }        |

| 2. Lab Applications                          | ŀ        |

| <u>3. Articulation Matrix</u> <u>5</u>       | <u>;</u> |

| <u>4. Mapping Justification</u> <u>5</u>     | <u>;</u> |

| 5. Curricular Gap and Content                | 5        |

| <u>6. Content Beyond Syllabus</u> 6          | 5        |

| C. COURSE ASSESSMENT                         | 5        |

| <u>1. Course Coverage</u> <u>6</u>           | <u>;</u> |

| 2. Continuous Internal Assessment (CIA)      | ,        |

| D. EXPERIMENTS                               | 2        |

| Experiment 01 : Structure of C program7      | ,        |

| Experiment 02 : Keywords and identifiers     |          |

| <u>Experiment 03 :</u>                       | )        |

| Experiment 04 :                              | )        |

|                                              | <u>)</u> |

Note : Remove "Table of Content" before including in CP Book

| (All all all all all all all all all all | SKIT      | Teaching Process  | Rev No.: 1.0    |

|------------------------------------------|-----------|-------------------|-----------------|

|                                          | Doc Code: | EC.SKIT.Ph5b1.F03 | Date:18-10-2019 |

|                                          | Title:    | Course Lab Manual | Page: 2 / 71    |

# **18ECL38 : DIGITAL ELECTRONICS LABORATORY**

### A. LABORATORY INFORMATION

#### 1. Lab Overview

| Degree:              | BE                               | Program:       | EC          |

|----------------------|----------------------------------|----------------|-------------|

| Year / Semester :    | 2/3                              | Academic Year: | 2019-20     |

| CourseTitle:         | DIGITAL SYSTEM DESIGN LABORATORY | Course Code:   | 18ECL38     |

| Credit / L-T-P:      | 2 / 1-0-1                        | SEE Duration:  | 180 Minutes |

| Total Contact Hours: | 36 Hrs                           | SEE Marks:     | 60Marks     |

| CIA Marks:           | 40                               | Assignment     | 1 / Module  |

| Course Plan Author:  | Mrs Kiranmayi M                  | Sign           | Dt :        |

| Checked By:          |                                  | Sign           | Dt :        |

#### 2. Lab Content

| Unit | Title of the Experiments                       | Lab Hours | Concept          | Blooms<br>Level |

|------|------------------------------------------------|-----------|------------------|-----------------|

| 1    | De-Morgan's law &Boolean expression relization | 03        | Demorgan's       | L3              |

|      | using logic gates                              |           | Theorem          | Understan       |

|      |                                                |           |                  | d               |

| 2    | FullAdderandSubtractor                         | 03        | Adder            | L4              |

|      |                                                |           | &Subtractor      | Analyze         |

| 3    | Parallel Adder/Subtractor using 7483           | 03        | Parallel         | L5              |

|      |                                                |           | Adder/Subtract   | Evaluate        |

|      |                                                |           | or               |                 |

| 4    | Comparators                                    | 03        | Comparators      | L5              |

| 5    | Multiplexer                                    | 03        | MUX              | L4              |

| 6    | Demultiplexerand Decoder                       | 03        | DEMUXand         | L4              |

|      |                                                |           | Decoder          |                 |

| 7    | Study of Flip-Flops                            | 03        | Flip-            | L3              |

|      |                                                |           | Flopverification |                 |

| 8    | ShiftRegisters                                 | 03        | ShiftRegisters   | L3              |

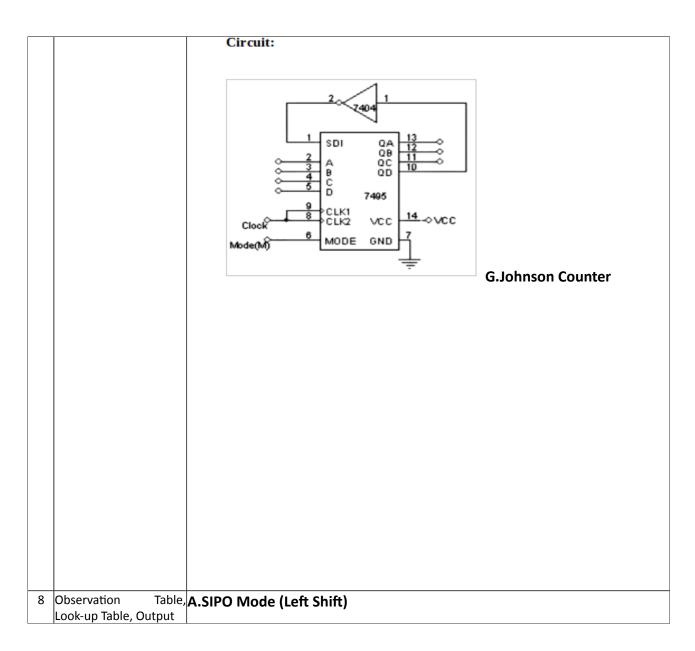

| 9    | RingCounter andJohnsonCounter                  | 03        | Ring/JohnsonC    | L3              |

|      |                                                |           | ounter           |                 |

| SKIT      | Teaching Process  | Rev No.: 1.0    |

|-----------|-------------------|-----------------|

| Doc Code: | EC.SKIT.Ph5b1.F03 | Date:18-10-2019 |

| Title:    | Course Lab Manual | Page: 3 / 71    |

| 10 | Synchronous Counters                             | 03 | Counters          | L3 |

|----|--------------------------------------------------|----|-------------------|----|

| 11 | Simulate Serial Adder using simulation tool.     | 03 | Serial- Adder     | L4 |

|    |                                                  |    | simulation        |    |

| 12 | Simulate Binary Multiplier using simulation tool | 03 | Binary Multiplier | L4 |

|    |                                                  |    |                   |    |

#### 3. Lab Material

| Unit | Details                                                                      | Available     |

|------|------------------------------------------------------------------------------|---------------|

| 1    | Text books                                                                   |               |

|      | 1. Digital Logic Applications and Design, John M Yarbrough, Thomson          | In Lib        |

|      | Learning,                                                                    |               |

|      | 2001. ISBN 981-240-062-1.                                                    |               |

|      | 2. Donald D. Givone, "Digital Principles and Design", Mc Graw Hill, 2002.    |               |

|      | ISBN 978-                                                                    |               |

|      | 0-07-052906-9.                                                               |               |

| 2    | Reference books                                                              |               |

|      | 1. D. P. Kothari and J. S Dhillon, "Digital Circuits and Design", Pearson,   | In dept       |

|      | 2016,                                                                        |               |

|      | ISBN:9789332543539.                                                          |               |

|      | 2. Morris Mano, —Digital design, Prentice Hall of India, Third Edition.      |               |

|      | 3. Charles H Roth, Jr., "Fundamentals of logic design", Cengage Learning.    |               |

|      | 4. K. A. Navas, "Electronics Lab Manual", Volume I, PHI, 5 th Edition, 2015, |               |

|      | ISBN:                                                                        |               |

|      | 9788120351424.                                                               |               |

| 3    | Others (Web, Video, Simulation, Notes etc.)                                  |               |

|      |                                                                              | Not Available |

|      |                                                                              |               |

## 4. Lab Prerequisites:

| -   | -       | Base Course:      |                                   | -   | -       |

|-----|---------|-------------------|-----------------------------------|-----|---------|

| SNo | Course  | Course Name       | Topic / Description               | Sem | Remarks |

|     | Code    |                   |                                   |     |         |

| 1   | 18ELN14 | Basic Electronics | Knowledge on Digital electronics, | 2   |         |

|     |         |                   | boolean laws, basic gates         |     |         |

|   | SKIT      | Teaching Process  | Rev No.: 1.0    |

|---|-----------|-------------------|-----------------|

| ) | Doc Code: | EC.SKIT.Ph5b1.F03 | Date:18-10-2019 |

|   | Title:    | Course Lab Manual | Page: 4 / 71    |

|  | Knowledge of Filp-flops | - | Plan Gap Course |

|--|-------------------------|---|-----------------|

|  |                         |   |                 |

|  |                         |   |                 |

|  |                         |   |                 |

Note: If prerequisites are not taught earlier, GAP in curriculum needs to be addressed. Include in Remarks and implement in B.5.

#### 5. General Instructions

| SNo | Instructions                                                            | Remarks |

|-----|-------------------------------------------------------------------------|---------|

| 1   | Observation book and Lab record are compulsory.                         |         |

| 2   | Students should report to the concerned lab as per the time table.      |         |

| 3   | After completion of the Experiment, certification/signof the concerned  |         |

|     | staff in-charge in the observation book is necessary.                   |         |

| 4   | Student should bring a notebook of 100 pages and should enter the       |         |

|     | readings /observations into the notebook while performing the           |         |

|     | experiment.                                                             |         |

| 5   | The record of observations along with the detailed experimental         |         |

|     | procedure of the experiment in the Immediate last session should be     |         |

|     | submitted and certified/signed bystaff member in-charge.                |         |

| 6   | Should attempt all Experiments/ assignments given in the                |         |

|     | experimentlist session wise.                                            |         |

| 7   | When the experiment is completed, should disconnect the setup made      |         |

|     | by them, and should return all the components/instruments taken for     |         |

|     | the purpose.                                                            |         |

| 8   | Any damage of the equipment or burn-out components will be viewed       |         |

|     | seriously either by putting penalty or by dismissing the total group of |         |

|     | students from the lab for the semester/year                             |         |

| 9   | Completed lab assignments should be submitted in the form of a Lab      |         |

|     | Record in which you have to write the logic diagrams, Truth table,      |         |

|     | expressions, simplification stepsand output for various inputs given    |         |

### 6. Lab Specific Instructions

| SNo | Specific Instructions                                              | Remarks |

|-----|--------------------------------------------------------------------|---------|

| 1   | Start writing the logic diagrams with the pin numbers              |         |

| 2   | Estimate the components required to perform the experiment (No. of |         |

|   | 1  | antes . |    | 1  |

|---|----|---------|----|----|

| 1 | 13 | 00      | R  |    |

|   | 10 | 5       | 參) | L) |

| 1 |    | 8       | 1  | 1  |

|   | SKIT      | Teaching Process  | Rev No.: 1.0    |

|---|-----------|-------------------|-----------------|

| ) | Doc Code: | EC.SKIT.Ph5b1.F03 | Date:18-10-2019 |

|   | Title:    | Course Lab Manual | Page: 5 / 71    |

|   | IC's, Pathcards)                                                   |

|---|--------------------------------------------------------------------|

| 3 | Use the trainer kit &Make the connections as per Logic diagram     |

| 4 | Turn on the power supply and check for the output                  |

| 5 | Check for the Errors in connection and correct it                  |

| 6 | Notedown the inputand output valuesand compare with original truth |

|   | table                                                              |

| 7 | Perform the Experiment for different inputs                        |

### **B. OBE PARAMETERS**

## 1. Lab / Course Outcomes

| # | COs                                     | Teach. | Concept      | Instr    | Assessment  | Blooms' |

|---|-----------------------------------------|--------|--------------|----------|-------------|---------|

|   |                                         | Hours  |              | Method   | Method      | Level   |

| 1 | Verify &understand De-Morgan's          | 03     | Demorgan's   | Demons   | Oral        | L3      |

|   | theorem &realize the boolean            |        | Theorem      | trate    | questions   | Underst |

|   | expression using logic gates            |        |              |          |             | and     |

| 2 | Analyze the full adder/subtractor logic | 03     | Full Adder   | Demons   | Oral        | L4      |

|   | using logic gates                       |        | &Subtractor  | trate    | question    | Analyze |

|   |                                         |        |              |          | and         |         |

|   |                                         |        |              |          | realization |         |

| 3 | Design the parallel adder &subtractor   | 03     | Parallel     | Demons   | Assignment  | L5      |

|   | circuits and compare both the circuits  |        | Adder/Subt   | trate    | and Slip    | Evaluat |

|   |                                         |        | ractor       |          | Test        | e       |

| 4 | Evaluate the performance of 4-bit       | 03     | Comparator   | Tutorial | Assignment  | L5      |

|   | magnitude comparator using 7485 IC      |        | S            |          |             |         |

| 5 | Realize 4:1 mux &8:1 mux and Analyze    | 03     | MUX          | Demons   |             | L4      |

|   | the both                                |        |              | trate    |             |         |

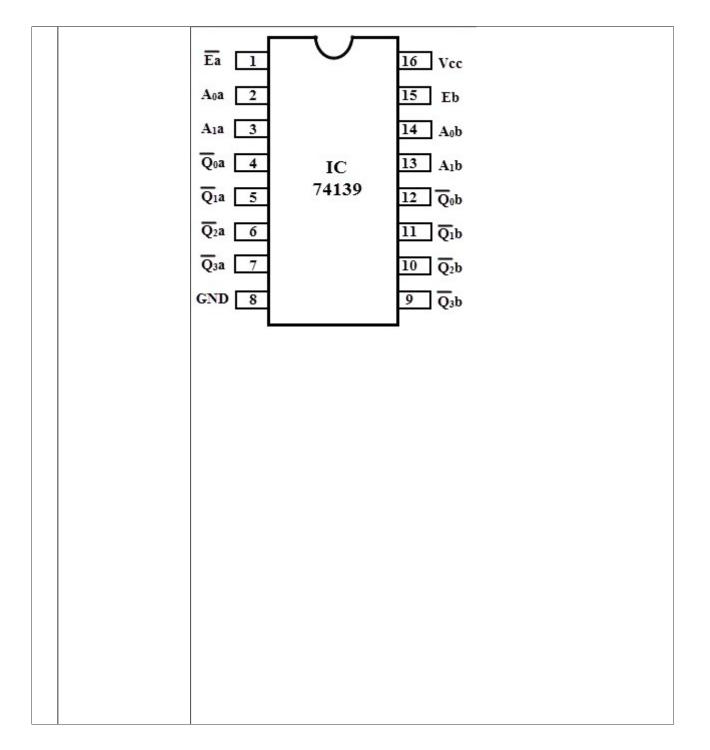

| 6 | Realize 1:8 Demux &3:8 Decoder using    | 03     | DEMUXand     | Tutorial | Assignment  | L4      |

|   | 74138 IC                                |        | Decoder      |          |             |         |

| 7 | Realize the operation of clocked SR &JK | 03     | Flip-        | Demons   | Assignment  | L3      |

|   | flip-flop.                              |        | Flopverifica | trate    | and Slip    |         |

|   |                                         |        | tion         |          | Test        |         |

| 8 | Understand the operation of shift       | 03     | ShiftRegiste | lecture  | Assignment  | L3      |

|   | registers                               |        | rs           |          |             |         |

| 9 | differentiate Ring counter &Johnson     | 03     | Ring/Johns   | Demons   | Assignment  | L3      |

|   |                                         | -      |              | •        |             | •       |

|   | ß | -  |    |    | 1  |

|---|---|----|----|----|----|

| 1 | ľ | 10 | al | 2  | 1  |

|   | 2 | =  | 39 |    | ě) |

| 3 | 0 | 1  | 5  | 10 | 1  |

| ] [ | SKIT      | Teaching Process  | Rev No.: 1.0    |

|-----|-----------|-------------------|-----------------|

|     | Doc Code: | EC.SKIT.Ph5b1.F03 | Date:18-10-2019 |

|     | Title:    | Course Lab Manual | Page: 6 / 71    |

|    | counter using 7476 IC                 |    | onCounter  | trate               |            |    |

|----|---------------------------------------|----|------------|---------------------|------------|----|

| 10 | Realize the 3 bit counters and verify | 03 | Counters   | Demons              | Oral       | L3 |

|    | with truth table                      |    |            | trate               | questions  |    |

| 11 | Analyze the Serial adder simulation   |    | Serial     | Simulati Assignment |            | L4 |

|    | process                               |    | simulation | on                  |            |    |

| 12 | Simulate the working of a Binary      | 03 | Binary     | Simulati            | Assignment | L4 |

|    | Multiplier                            |    | Multiplier | on                  |            |    |

| -  | Total                                 | 36 | -          | -                   | -          | -  |

Note: Identify a max of 2 Concepts per unit. Write 1 CO per concept.

## 2. Lab Applications

| SNo | Application Area                                                            | CO   | Level  |

|-----|-----------------------------------------------------------------------------|------|--------|

| 1   | Engineering – Building circuits,Set Theory – Venn diagrams, Java            | CO1  | L3     |

|     |                                                                             |      | Under  |

|     |                                                                             |      | stand  |

| 2   | integrated in the calculators and At Networking side the Full adder is used | CO2  | L4     |

|     | mostly.                                                                     |      | Analyz |

|     |                                                                             |      | e      |

| 3   | CPLD applications and VHDL circuits and devices                             | CO3  | L5     |

|     |                                                                             |      | Evalua |

|     |                                                                             |      | te     |

| 4   | Generally, in electronics, the comparatoris used to compare two voltages or | CO4  | L5     |

|     | currents                                                                    |      |        |

| 5   | Communication System for the process of data transmission.                  | CO5  | L4     |

| 6   | Communication System which converts multiplexed signals back to the         | CO6  | L4     |

|     | original form/ wireless or wired media                                      |      |        |

| 7   | main components of sequential circuitsm, storing of binary data, counter,   | C07  | L3     |

|     | transferring binary data from one location to other                         |      |        |

| 8   | Temporary data storage, Data transfer, Data manipulation And incounters.    | CO8  | L3     |

|     |                                                                             |      |        |

| 9   | count the data in a continuous loop, used in frequency divider circuits, 3  | CO9  | L3     |

|     | phase square wave generator , BCD counter etc                               |      |        |

| 10  | Alarm clock, Set an AC timer, Set a timer for taking picture, finite state  | CO10 | L3     |

|     | machines etc                                                                |      |        |

| (Sameren | SKIT      | Teaching Process  | Rev No.: 1.0    |

|----------|-----------|-------------------|-----------------|

|          | Doc Code: | EC.SKIT.Ph5b1.F03 | Date:18-10-2019 |

|          | Title:    | Course Lab Manual | Page: 7 / 71    |

| 11 | Engineering - Building circuits,Set Theory - Venn diagrams | CO11 | L4 |

|----|------------------------------------------------------------|------|----|

| 12 | dividers for clock signals, finite state machines etc      | CO12 | L4 |

|    |                                                            |      |    |

Note: Write 1 or 2 applications per CO.

#### 3. Articulation Matrix

## (CO – PO MAPPING)

| -          | Course Outcomes                                                                              |     |     |     |     |     | ram ( |             |     |     |          | _        |          |       |

|------------|----------------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-------|-------------|-----|-----|----------|----------|----------|-------|

| #          | COs                                                                                          | PO1 | PO2 | PO3 | PO4 | PO5 | PO6   | P <b>O7</b> | PO8 | PO9 | PO1<br>0 | PO1<br>1 | PO1<br>2 | Level |

| 18ECL38.1  | Verify & understand De-Morgan's theorem & realize the boolean                                |     | 2   | 2   |     |     |       |             |     |     |          |          |          | L3    |

| 18ECL38.2  | expression using logic gates<br>Analyze the full adder/subtractor logic<br>using logic gates | 3   | 2   | 2   |     |     |       |             |     |     |          |          |          | L3    |

| 18ECL38.3  | Design the parallel adder & subtractor circuits and compare both the circuits                | 3   | 2   | 2   |     |     |       |             |     |     |          |          |          | L3    |

| 18ECL38.4  | Evaluate the performance of 4-bit magnitude comparator using 7485 IC                         | 3   | 2   | 2   |     |     |       |             |     |     |          |          |          | L3    |

| 18ECL38.5  | Realize 4:1 mux &8:1 mux and Analyze the both                                                | 3   | 2   | 2   |     |     |       |             |     |     |          |          |          | L3    |

| 18ECL38.6  | Realize 1:8 Demux &3:8 Decoder using 74138 IC                                                | 3   | 2   | 2   |     |     |       |             |     |     |          |          |          | L3    |

|            | Realize the operation of clocked SR &JK<br>flip-flop.                                        | 3   | 2   | 2   |     |     |       |             |     |     |          |          |          | L3    |

| 18ECL38.8  | Understand the operation of shift registers                                                  | 3   | 2   | 2   |     |     |       |             |     |     |          |          |          | L3    |

| 18ECL38.9  | differentiate Ring counter &Johnson<br>counter using 7476 IC                                 | 3   | 2   | 2   |     |     |       |             |     |     |          |          |          | L3    |

| 18ECL38.10 | Realize the 3 bit counters and verify with truth table                                       | 3   | 2   | 2   |     |     |       |             |     |     |          |          |          | L3    |

| 18ECL38.11 | Analyze the Serial adder simulation process                                                  | 3   | 2   | 2   |     | 2   |       |             |     |     |          |          |          | L3    |

| 18ECL38.12 | Simulate the working of Binary<br>Multiplier                                                 | 3   | 2   | 2   |     | 2   |       |             |     |     |          |          |          | L3    |

| 18ECL38    | Average                                                                                      | 3   | 2   | 2   |     | 2   |       |             |     |     |          |          |          |       |

Note: Mention the mapping strength as 1, 2, or 3

### 4. Mapping Justification

| SKIT      | Teaching Process  | Rev No.: 1.0    |

|-----------|-------------------|-----------------|

| Doc Code: | EC.SKIT.Ph5b1.F03 | Date:18-10-2019 |

| Title:    | Course Lab Manual | Page: 8 / 71    |

| Mappi | ng  | Mapping<br>Level | Justification                                                         |

|-------|-----|------------------|-----------------------------------------------------------------------|

| СО    | PO  | -                | -                                                                     |

| C01   | PO1 | L1               | Basic knowledge of mathematics is essential to understand the         |

|       |     |                  | combinatorial circuit design to build complex system like processor.  |

| C01   | PO2 | L2               | Simple mathematical analysis is required to build complex system      |

|       |     |                  | like micro-controllers using combinatorial logic.                     |

| C01   | PO3 | L2               | Strong foundation in designing and modeling of combinatorial logic    |

|       |     |                  | circuits enables to provide design solutions for complex engineering  |

|       |     |                  | problems like Arithmetic and logic units.                             |

| CO2   | PO1 | L1               | Basic knowledge of mathematics is essential to design adder and       |

|       |     |                  | subtractors which are used in building complex system like Digital    |

|       |     |                  | signal processors and ASIC's.                                         |

| CO2   | PO2 | L2               | Simple mathematical analysis is required to build complex system like |

|       |     |                  | DSP Processors using basic adder and subtractors.                     |

| CO2   | PO3 | L2               | Strong foundation in designing adder and subtractor circuits enables  |

|       |     |                  | to provide design solutions for complex engineering problems like     |

|       |     |                  | ASIC's and high speed processors.                                     |

| CO3   | PO1 | L1               | Basic knowledge of mathematics is essential to design adder and       |

|       |     |                  | subtractors which are used in building complex system like Digital    |

|       |     |                  | signal processors and ASIC's.                                         |

| CO3   | PO2 | L2               | Simple mathematical analysis is required to build complex system like |

|       |     |                  | DSP Processors using basic adder and subtractors.                     |

| CO3   | PO3 | L2               | Strong foundation in designing adder and subtractor circuits enables  |

|       |     |                  | to provide design solutions for complex engineering problems like     |

|       |     |                  | ASIC's and high speed processors.                                     |

| CO4   | PO1 | L1               | Basic knowledge of mathematics is essential to design comparator      |

|       |     |                  | which are used in building complex system like Digital signal         |

|       |     |                  | processors and ASIC's.                                                |

| CO4   | PO2 | L2               | Simple mathematical analysis is required to build complex system like |

|       |     |                  | DSP Processors using basic comparators.                               |

| CO4   | PO3 | L2               | Strong foundation in designing comparator circuits enables to provide |

|       |     |                  | design solutions for complex engineering problems like ASIC's and     |

|       |     |                  | high speed processors.                                                |

| SKIT      | Teaching Process  | Rev No.: 1.0    |

|-----------|-------------------|-----------------|

| Doc Code: | EC.SKIT.Ph5b1.F03 | Date:18-10-2019 |

| Title:    | Course Lab Manual | Page: 9 / 71    |

| CO5  | PO1 | L1 | Basic knowledge of mathematics is essential to design multiplexers which are used in building complex system like processor.                                  |

|------|-----|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CO5  | PO2 | L2 | Simple mathematical analysis is required to build complex system like micro-controllers using combinational circuits like multiplexers                        |

| CO5  | PO3 | L2 | Strong foundation in designing combinational circuits enables to provide design solutions for complex engineering problems like Arithmetic and logic units.   |

| CO6  | PO1 | L1 | Basic knowledge of mathematics is essential to design decoders and de-multiplexers which are used in building complex system like processor.                  |

| CO6  | PO2 | L2 | Simple mathematical analysis is required to build complex system<br>like micro-controllers using combinational circuits like decoders and<br>de-multiplexers. |

| CO6  | PO3 | L2 | Strong foundation in designing combinational circuits enables to provide design solutions for complex engineering problems like Arithmetic and logic units.   |

| C0`7 | PO1 | L1 | Basic knowledge of mathematics is essential to design flip-flop which are used in building complex system like memories.                                      |

| C07  | PO2 | L2 | Simple mathematical analysis is required to build complex system like micro-controllers using basic flip flops.                                               |

| C07  | PO3 | L2 | Strong foundation in designing flip-flop circuits enables to provide design solutions for complex engineering problems like memories.                         |

| CO8  | PO1 | L1 | Basic knowledge of mathematics is essential to design shift registers which are used in building complex system like memories.                                |

| CO8  | PO2 | L2 | Simple mathematical analysis is required to build complex system like micro-controllers using basic shift registers.                                          |

| C08  | PO3 | L2 | Strong foundation in designing shift registers circuits enables to provide design solutions for complex engineering problems like memories.                   |

| CO9  | PO1 | L1 | Basic knowledge of mathematics is essential to design counters which are used in building complex system in medical field like ECG counter.                   |

| CO9  | PO2 | L2 | Simple mathematical analysis is required to build complex system like micro-controllers, timers using basic counters.                                         |

| SKIT      | Teaching Process  | Rev No.: 1.0    |

|-----------|-------------------|-----------------|

| Doc Code: | EC.SKIT.Ph5b1.F03 | Date:18-10-2019 |

| Title:    | Course Lab Manual | Page: 10 / 71   |

| CO9  | PO3 | L2 | Strong foundation in designing counter circuits enables to provide design solutions for complex engineering problems like timers and counters in processors and controllers.                    |

|------|-----|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CO10 | PO1 | L1 | Basic knowledge of mathematics is essential to design counters which<br>are used in building complex system in medical field like ECG<br>counter.                                               |

| CO10 | PO2 | L2 | Simple mathematical analysis is required to build complex system like micro-controllers, timers using basic counters.                                                                           |

| CO10 | PO3 | L2 | Strong foundation in designing counter circuits enables to provide design solutions for complex engineering problems like timers and counters in processors and controllers.                    |

| CO11 | PO1 | L1 | Basic knowledge of mathematics is essential to design adder and<br>subtractors which are used in building complex system like Digital<br>signal processors and ASIC's.                          |

| C011 | PO2 | L2 | Simple mathematical analysis is required to build complex system like DSP Processors using basic adder and subtractors.                                                                         |

| C011 | PO3 | L2 | Strong foundation in designing adder and subtractor circuits enables<br>to provide design solutions for complex engineering problems like<br>ASIC's and high speed processors.                  |

| C011 | PO5 | L2 | Modern tool Multisim is used for designing the adder and subtractor circuits which can be used to model complex circuits used in building complex system like ASIC's and high speed processors. |

| C012 | PO1 | L1 | Basic knowledge of mathematics is essential to design counters which<br>are used in building complex system in medical field like ECG<br>counter.                                               |

| CO12 | PO2 | L2 | Simple mathematical analysis is required to build complex system like micro-controllers, timers using basic counters.                                                                           |

| CO12 | PO3 | L2 | Strong foundation in designing counter circuits enables to provide design solutions for complex engineering problems like timers and counters in processors and controllers.                    |

| C012 | PO5 | L2 | Modern tool Multisim is used for designing the counter circuits which<br>can be used to model complex circuits used in building complex<br>system like ASIC's and high speed processors.        |

Note: Write justification for each CO-PO mapping.

| (And the second | SKIT      | Teaching Process  | Rev No.: 1.0    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------------|-----------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Doc Code: | EC.SKIT.Ph5b1.F03 | Date:18-10-2019 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Title:    | Course Lab Manual | Page: 11 / 71   |

#### 5. Curricular Gap and Content

| SNo | Gap Topic | Actions Planned | Schedule Planned | Resources Person | PO Mapping |

|-----|-----------|-----------------|------------------|------------------|------------|

| 1   |           |                 |                  |                  |            |

| 2   |           |                 |                  |                  |            |

Note: Write Gap topics from A.4 and add others also.

## 6. Content Beyond Syllabus

| SNo | Gap Topic | Actions Planned | Schedule Planned | Resources Person | PO Mapping |

|-----|-----------|-----------------|------------------|------------------|------------|

| 1   |           |                 |                  |                  |            |

| 2   |           |                 |                  |                  |            |

|     |           |                 |                  |                  |            |

|     |           |                 |                  |                  |            |

Note: Anything not covered above is included here.

#### C. COURSE ASSESSMENT

### 1. Course Coverage

| Unit | Title                           | Teachin |       | N     | o. of q | uestion | in Exai | n     |     | СО   | Levels |

|------|---------------------------------|---------|-------|-------|---------|---------|---------|-------|-----|------|--------|

|      |                                 | g Hours | CIA-1 | CIA-2 | CIA-3   | Asg-1   | Asg-2   | Asg-3 | SEE |      |        |

| 1    | De-Morgan's law &Boolean        | 03      | 1     | -     | -       | -       | -       | -     | 1   | CO1  |        |

|      | expression relization using     |         |       |       |         |         |         |       |     |      |        |

|      | logic gates                     |         |       |       |         |         |         |       |     |      |        |

| 2    | FullAdderandSubtractor          | 03      | 1     | -     | -       | -       | -       | -     | 1   | CO2  |        |

| 3    | Parallel Adder/Subtractor using | 03      | 1     | -     | -       | -       | -       | -     | 1   | CO3  |        |

|      | 7483                            |         |       |       |         |         |         |       |     |      |        |

| 4    | Comparators                     | 03      | 1     | -     | -       | -       | -       | -     | 1   | CO4  |        |

| 5    | Multiplexer                     | 03      | 1     | -     | -       | -       | -       | -     | 1   | CO5  |        |

| 6    | Demultiplexerand Decoder        | 03      | 1     | -     | -       | -       | -       | -     | 1   | CO6  |        |

| 7    | Study of Flip-Flops             | 03      | -     | 1     | -       | -       | -       | -     | 1   | C07  |        |

| 8    | ShiftRegisters                  | 03      | I     | 1     | -       | -       |         | -     | 1   | CO8  |        |

| 9    | RingCounter                     | 03      | -     | 1     | -       | -       | -       | -     | 1   | CO9  |        |

|      | andJohnsonCounter               |         |       |       |         |         |         |       |     |      |        |

| 10   | Counters                        | 03      | -     | -     | 1       | -       | -       | -     | 1   | CO10 |        |

| 11   | Simulate Serial- Adder using    | 03      | -     | -     | 1       | -       | _       | -     | 1   | CO11 |        |

|      | simulation tool.                |         |       |       |         |         |         |       |     |      |        |

| 1   | an th | wite. | 10 |

|-----|-------|-------|----|

| (II | 10    | al    | X  |

|     |       | 18    |    |

| 6   | 1     | 5     | 19 |

| 6   |       | 410   | Ì  |

|   | SKIT      | Teaching Process  | Rev No.: 1.0    |

|---|-----------|-------------------|-----------------|

|   | Doc Code: | EC.SKIT.Ph5b1.F03 | Date:18-10-2019 |

| / | Title:    | Course Lab Manual | Page: 12 / 71   |

| 12 | Simulate Binary Multiplier using | 03 | - | - | 1 | - | - | - | 1  | CO12 |   |

|----|----------------------------------|----|---|---|---|---|---|---|----|------|---|

|    | simulation tool.                 |    |   |   |   |   |   |   |    |      |   |

| -  | Total                            | 36 | 6 | 3 | 3 |   |   |   | 12 | -    | - |

Note: Write CO based on the theory course.

## 2. Continuous Internal Assessment (CIA)

| Evaluation                      | Weightage in Marks | СО                      | Levels     |

|---------------------------------|--------------------|-------------------------|------------|

| CIA Exam – 1                    | 30                 | CO1, CO2, CO3, CO4      | L23, L3    |

| CIA Exam – 2                    | 30                 | CO5, CO6, CO7,          | L1, L2, L3 |

| CIA Exam – 3                    | 30                 | CO8, CO9                | L1, L2, L3 |

|                                 |                    |                         |            |

| Assignment - 1                  | 05                 | CO1, CO2, CO3, CO4      | L2, L3, L4 |

| Assignment - 2                  | 05                 | CO5, CO6, CO7, CO8, CO9 | L1, L2, L3 |

| Assignment - 3                  | 05                 | CO8, CO9                | L1, L2, L3 |

|                                 |                    |                         |            |

| Seminar - 1                     | 05                 | CO1, CO2, CO3, CO4      | L2, L3, L4 |

| Seminar - 2                     | 05                 | CO5, CO6,CO7,CO8, CO9   | L2, L3, L4 |

| Seminar - 3                     | 05                 | CO8, CO9                | L2, L3, L4 |

|                                 |                    |                         |            |

| Other Activities – define –Slip |                    | CO1 to Co9              | L2, L3, L4 |

| test                            |                    |                         |            |

| Final CIA Marks                 | 40                 | -                       | -          |

| SNo | Description                                  | Marks                  |

|-----|----------------------------------------------|------------------------|

| 1   | Observation and Weekly Laboratory Activities | 05 Marks               |

| 2   | Record Writing                               | 10 Marks for each Expt |

| 3   | Internal Exam Assessment                     | 25 Marks               |

| 4   | Internal Assessment                          | 40 Marks               |

| 5   | SEE                                          | 60Marks                |

| -   | Total                                        | 100 Marks              |

#### D. EXPERIMENTS

\_

# Experiment 01 : De-Morgan's law & Boolean expression relization using logic gates

| - | Experiment No.: | 1 | Marks      |       | Date P  | lanned |          | Date<br>Conducted | 1     |       |

|---|-----------------|---|------------|-------|---------|--------|----------|-------------------|-------|-------|

| 1 | Title           | D | e-Morgan's | a law | &Boolea | n ex   | oression | relization        | using | logic |

| SKIT      | Teaching Process  | Rev No.: 1.0    |

|-----------|-------------------|-----------------|

| Doc Code: | EC.SKIT.Ph5b1.F03 | Date:18-10-2019 |

| Title:    | Course Lab Manual | Page: 13 / 71   |

|   |                    | gates                                                                                                                                   |

|---|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 2 | Course Outcomes    | Verify &understand De-Morgan's theorem &realize the boolean expression using logic                                                      |

| 2 | Course Outcomes    | gates                                                                                                                                   |

| 3 | Aim                | To verify                                                                                                                               |

|   |                    | a) De-Morgan's theorem for 2-variables                                                                                                  |

|   |                    | b) The Sum-of-Product and Product-of-sum expression using                                                                               |

|   |                    | universal gates                                                                                                                         |

| 4 |                    | Lab Manual                                                                                                                              |

|   | Required           | IC 7408 (AND), IC 7404 (NOT), IC 7432 (OR),IC 7400 (NAND),                                                                              |

|   |                    | IC7402 (NOR),IC 7486 (EX-OR)                                                                                                            |

| 5 |                    | Given Problem:                                                                                                                          |

|   | Principle, Concept | $Y = f \ A, B, C, D = \overline{ABCD} + \overline{ABCD} + \overline{ABCD} + \overline{ABCD} + ABC\overline{D} + ABC\overline{D} + ABCD$ |

|   |                    |                                                                                                                                         |

| 6 | Procedure          | 1.Verify that the gates areworking.                                                                                                     |

|   |                    | 1.verny that the gates are working.                                                                                                     |

|   |                    | 2.Constructa truth table for the given problem.                                                                                         |

|   |                    |                                                                                                                                         |

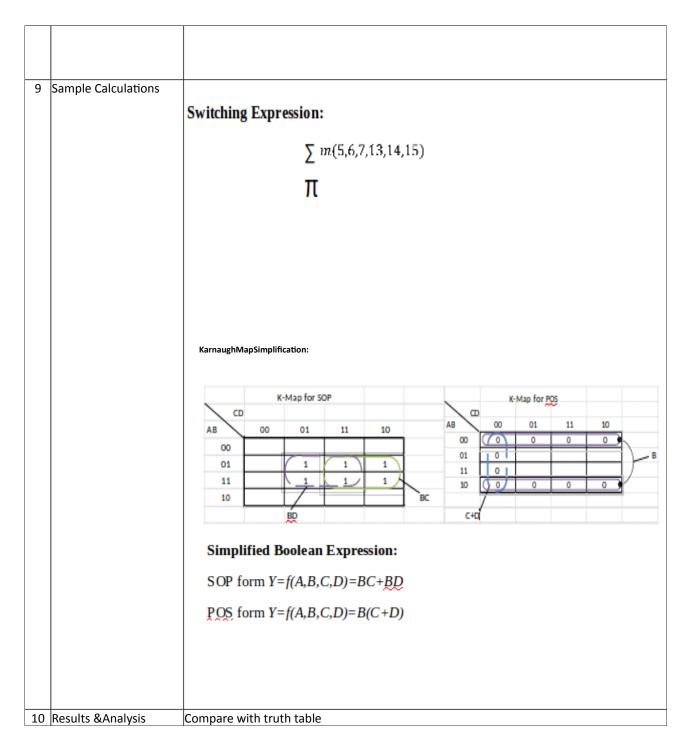

|   |                    | 3.Draw a Karnaugh Mapcorresponding to the given truth table.                                                                            |

|   |                    |                                                                                                                                         |

|   |                    | 4.Simplify the given Boolean expressionmanuallyusing the Karnaugh Map.                                                                  |

|   |                    |                                                                                                                                         |

|   |                    | Administration Uning Logic Cotos                                                                                                        |

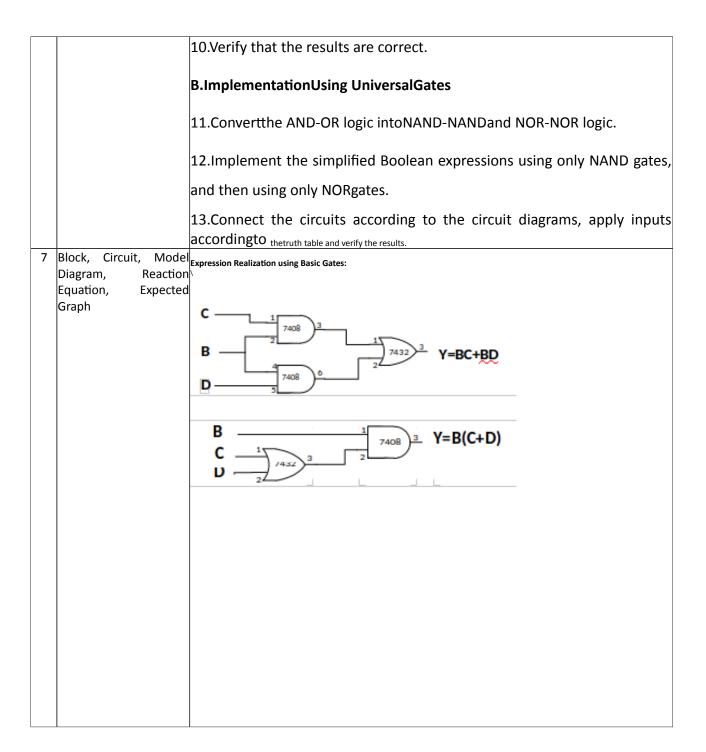

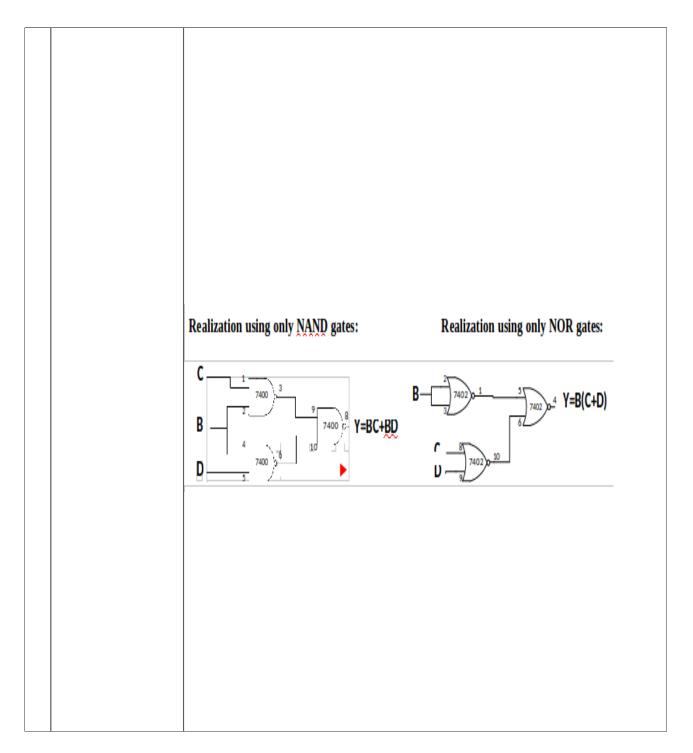

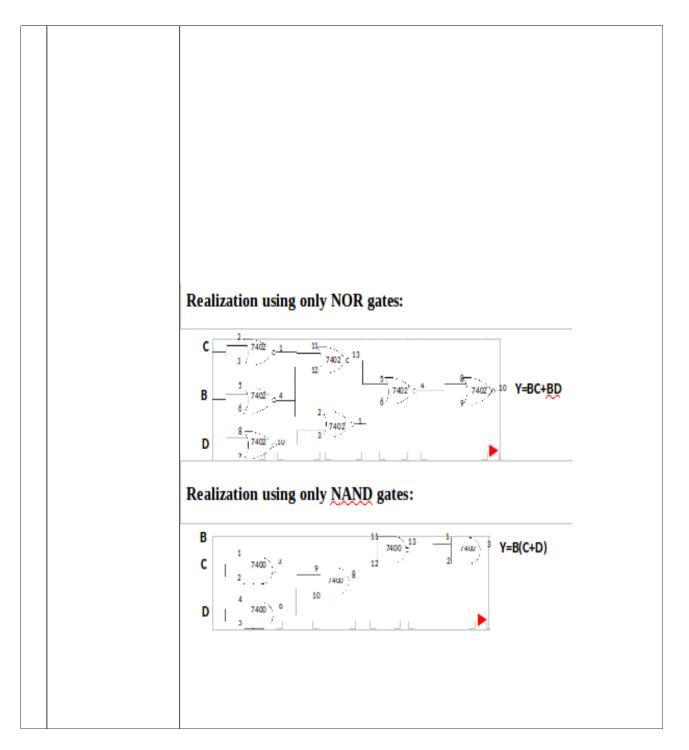

|   |                    | A:ImplementationUsing Logic Gates                                                                                                       |

|   |                    | 5.Realizethe simplified expression using logic gates.                                                                                   |

|   |                    |                                                                                                                                         |

|   |                    | 6.Connect V <sub><math>\alpha</math></sub> andground as shown in the pin diagram.                                                       |

|   |                    |                                                                                                                                         |

|   |                    | 7.Make connections as per the logic gate diagram.                                                                                       |

|   |                    |                                                                                                                                         |

|   |                    | 8.Apply the different combinations of input according to the truth tables.                                                              |

|   |                    |                                                                                                                                         |

|   |                    | 9.Check the output readings for the given circuits; check themagainst the truth tables.                                                 |

|   |                    | נו ענוז נמטוכא.                                                                                                                         |

|   |                    | 1                                                                                                                                       |

| (And And And And And And And And And And | SKIT      | Teaching Process  | Rev No.: 1.0    |

|------------------------------------------|-----------|-------------------|-----------------|

|                                          | Doc Code: | EC.SKIT.Ph5b1.F03 | Date:18-10-2019 |

|                                          | Title:    | Course Lab Manual | Page: 14 / 71   |

|   | 1  | and a | ane. |                     |   |

|---|----|-------|------|---------------------|---|

| 1 | 7  | 00    | -    | 36                  | Ì |

|   | 1  |       | -    | $\langle 1 \rangle$ |   |

| X | 11 |       |      | 74                  | į |

| 1 |    | 3     | 2    |                     |   |

| SKIT      | Teaching Process  | Rev No.: 1.0    |

|-----------|-------------------|-----------------|

| Doc Code: | EC.SKIT.Ph5b1.F03 | Date:18-10-2019 |

| Title:    | Course Lab Manual | Page: 15 / 71   |

| 1 |

|---|

| 1 |

| 1 |

|   |

| SKIT      | Teaching Process  | Rev No.: 1.0    |

|-----------|-------------------|-----------------|

| Doc Code: | EC.SKIT.Ph5b1.F03 | Date:18-10-2019 |

| Title:    | Course Lab Manual | Page: 16 / 71   |

| SKIT      | Teaching Process  | Rev No.: 1.0    |

|-----------|-------------------|-----------------|

| Doc Code: | EC.SKIT.Ph5b1.F03 | Date:18-10-2019 |

| Title:    | Course Lab Manual | Page: 17 / 71   |

|   | 1  | anti- | ane. |                     |   |

|---|----|-------|------|---------------------|---|

| 1 | 7  | 00    | -    | 36                  | Ì |

|   | 1  |       | -    | $\langle 1 \rangle$ |   |

| X | 11 |       |      | 74                  | į |

| 1 |    | 1     | 2    |                     |   |

| SKIT      | Teaching Process  | Rev No.: 1.0    |

|-----------|-------------------|-----------------|

| Doc Code: | EC.SKIT.Ph5b1.F03 | Date:18-10-2019 |

| Title:    | Course Lab Manual | Page: 18 / 71   |

| 8        | TruthTable, Output |  |

|----------|--------------------|--|

| <u> </u> |                    |  |

| SKIT      | Teaching Process  | Rev No.: 1.0    |

|-----------|-------------------|-----------------|

| Doc Code: | EC.SKIT.Ph5b1.F03 | Date:18-10-2019 |

| Title:    | Course Lab Manual | Page: 19 / 71   |

|  | ,  |     |     |      |   |

|--|----|-----|-----|------|---|

|  | Tr | uth | Tal | ole: |   |

|  |    |     |     | -    |   |

|  | A  | В   | С   |      | Y |

|  | 0  | 0   | 0   | 0    | 0 |

|  | 0  | 0   | 0   | 1    | 0 |

|  | 0  | 0   | 1   | 0    | 0 |

|  | 0  | 0   | 1   | 1    | 0 |

|  | 0  | 1   | 0   | 0    | 0 |

|  | 0  | 1   | 0   | 1    | 1 |

|  | 0  | 1   | 1   | 0    | 1 |

|  | 0  | 1   | 1   | 1    | 1 |

|  | 1  | 0   | 0   | 0    | 0 |

|  | 1  | 0   | 0   | 1    | 0 |

|  | 1  | 0   | 1   | 0    | 0 |

|  | 1  | 0   | 1   | 1    | 0 |

|  | 1  | 1   | 0   | 0    | 0 |

|  | 1  | 1   | 0   | 1    | 1 |

|  | 1  | 1   | 1   | 0    | 1 |

|  | 1  | 1   | 1   | 1    | 1 |

|  |    |     |     |      |   |

|  |    |     |     |      |   |

|  |    |     |     |      |   |

|  |    |     |     |      |   |

|  |    |     |     |      |   |

|  |    |     |     |      |   |

|  |    |     |     |      |   |

|  |    |     |     |      |   |

|  |    |     |     |      |   |

|  |    |     |     |      |   |

|  |    |     |     |      |   |

|  |    |     |     |      |   |

|  |    |     |     |      |   |

|  |    |     |     |      |   |

|  |    |     |     |      |   |

|  |    |     |     |      |   |

|  |    |     |     |      |   |

|  |    |     |     |      |   |

|  |    |     |     |      |   |

|  |    |     |     |      |   |

|  |    |     |     |      |   |

|   | 1 | 1  | uter |   |   |

|---|---|----|------|---|---|

|   | Ø | 1  | 00.  |   |   |

| ( | 1 | 6  |      |   |   |

|   |   | 5  | Ł    | 2 | 9 |

|   | 1 | 24 | RIAL |   | 1 |

| SKIT      | Teaching Process  | Rev No.: 1.0    |

|-----------|-------------------|-----------------|

| Doc Code: | EC.SKIT.Ph5b1.F03 | Date:18-10-2019 |

| Title:    | Course Lab Manual | Page: 20 / 71   |

| · | SKIT      | Teaching Process  | Rev No.: 1.0    |

|---|-----------|-------------------|-----------------|

|   | Doc Code: | EC.SKIT.Ph5b1.F03 | Date:18-10-2019 |

|   | Title:    | Course Lab Manual | Page: 21 / 71   |

| 11 | Application Areas      | Engineering – Building circuits,Set Theory – Venn diagrams, Java |

|----|------------------------|------------------------------------------------------------------|

| 12 | Remarks                |                                                                  |

| 13 | Faculty Signature with |                                                                  |

|    | Date                   |                                                                  |

# Experiment 02 : Full Adder and Subtractor

| - | Experiment No.:      | 2               | Marks                                                 | Date Planned                          | Date<br>Conducted |  |  |  |  |  |

|---|----------------------|-----------------|-------------------------------------------------------|---------------------------------------|-------------------|--|--|--|--|--|

| 1 | Title                | Full            | ullAdderandSubtractor                                 |                                       |                   |  |  |  |  |  |

| 2 | Course Outcomes      | Analyz          | e the full add                                        | er/subtractor logic using logic gates |                   |  |  |  |  |  |

| 3 | Aim                  |                 | o realize half/fulladder and half/fullsubtractorusing |                                       |                   |  |  |  |  |  |

| 4 | Material / Equipment |                 | -                                                     |                                       |                   |  |  |  |  |  |

|   | Required             |                 |                                                       | 2, IC 7486, IC 7404, etc.             |                   |  |  |  |  |  |

| 5 | Theory, Formula,     |                 |                                                       |                                       |                   |  |  |  |  |  |

|   | Principle, Concept   | <u>S</u> = A⊕B⊕ |                                                       | В                                     |                   |  |  |  |  |  |

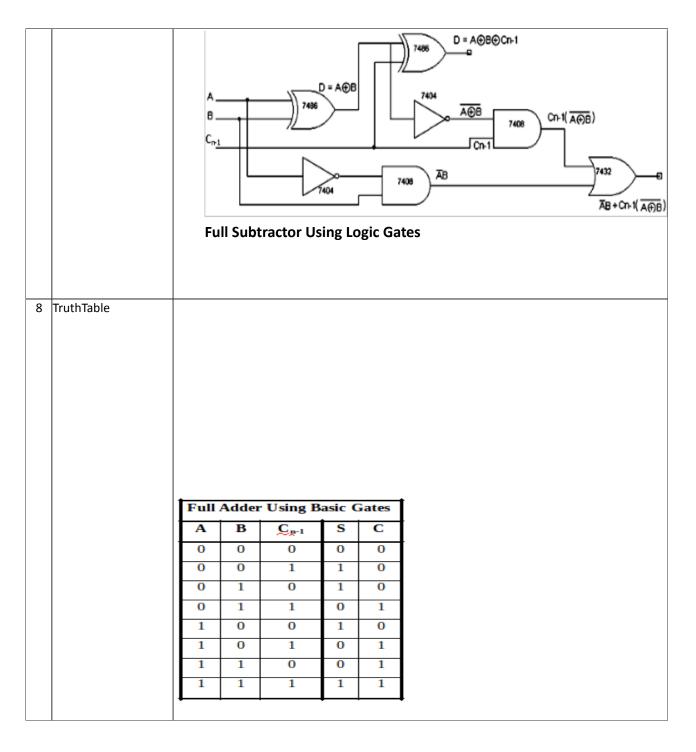

|   |                      | D = A(          | btractor:<br>⊚B⊛Cn-1<br>Cn-1(A⊕B)                     |                                       |                   |  |  |  |  |  |

EC Prepared by Approved

| SKIT               |       |

|--------------------|-------|

| Doc Code:          | EC.Sk |

| Title <sup>.</sup> | Cour  |

| SKIT      | Teaching Process  | Rev No.: 1.0    |  |

|-----------|-------------------|-----------------|--|

| Doc Code: | EC.SKIT.Ph5b1.F03 | Date:18-10-2019 |  |

| Title:    | Course Lab Manual | Page: 22 / 71   |  |

| 6 | Procedure, Program,<br>Activity, Algorithm,                      | 1.Verify that the gates areworking.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|---|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|   | Pseudo Code                                                      | 2. Make the connections as per the circuit diagram for the fulladder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|   |                                                                  | circuit, on thetrainer kit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|   |                                                                  | 3. Switchon the VCC powers upply and apply the various combinations o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|   |                                                                  | ftheinputs according tothe respective truth tables.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|   |                                                                  | 4. Note down the output readings for the full adder circuit for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|   |                                                                  | the corresponding combination of inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|   |                                                                  | 5.Verify that the outputs are accordingto the expected results.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|   |                                                                  | 6.Repeattheprocedureforfullsubtractor circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|   |                                                                  | 7.Verifythatthesum/differenceandcarry/borrowbitsareaccordingtothee xpected values.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| 7 | Block, Circuit, Model<br>Diagram, Reaction<br>Equation, Expected | Full Adder Using Logic Gates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|   | Graph                                                            | $A \oplus B \oplus Cr-1$ |  |  |  |  |  |

| (Samera) | SKIT      | Teaching Process  | Rev No.: 1.0    |

|----------|-----------|-------------------|-----------------|

|          | Doc Code: | EC.SKIT.Ph5b1.F03 | Date:18-10-2019 |

|          | Title:    | Course Lab Manual | Page: 23 / 71   |

| SKIT      | Teaching Process  | Rev No.: 1.0    |

|-----------|-------------------|-----------------|

| Doc Code: | EC.SKIT.Ph5b1.F03 | Date:18-10-2019 |

| Title:    | Course Lab Manual | Page: 24 / 71   |

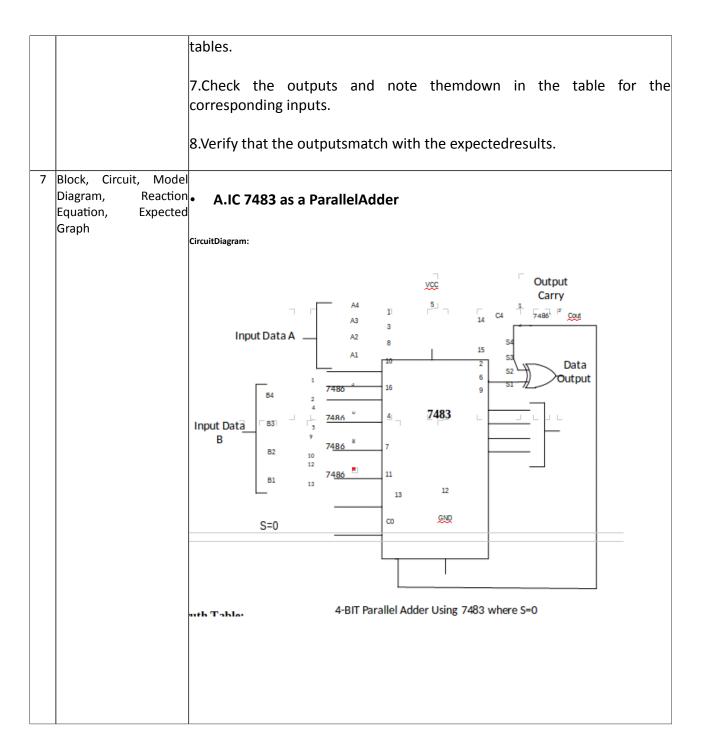

|  |   | Full Subtra | ictor Using I    | Basic Gates |   |

|--|---|-------------|------------------|-------------|---|

|  | A | В           | C <sub>n-1</sub> | D           | В |

|  | 0 | 0           | 0                | 0           | 0 |

|  | 0 | 0           | 1 0              | 1           | 1 |

|  | 0 | 1           | 1                | 0           | 1 |

|  | 1 | 0           | 0                | 1           | 0 |

|  | 1 | 0           | 1                | 0           | 0 |

|  | 1 | 1           | 0                | 0           | 0 |

|  | 1 | 1           | 1                | 1           | 1 |

|  | • |             |                  |             |   |

|  |   |             |                  |             |   |

|  |   |             |                  |             |   |

|  |   |             |                  |             |   |

|  |   |             |                  |             |   |

|  |   |             |                  |             |   |

|  |   |             |                  |             |   |

|  |   |             |                  |             |   |

|  |   |             |                  |             |   |

|  |   |             |                  |             |   |

|  |   |             |                  |             |   |

|  |   |             |                  |             |   |

| (All all all all all all all all all all | SKIT      | Teaching Process  | Rev No.: 1.0    |

|------------------------------------------|-----------|-------------------|-----------------|

|                                          | Doc Code: | EC.SKIT.Ph5b1.F03 | Date:18-10-2019 |

|                                          | Title:    | Course Lab Manual | Page: 25 / 71   |

| 9  | Sample Calculations    | -                                                                                   |

|----|------------------------|-------------------------------------------------------------------------------------|

| 10 | Results & Analysis     | Compare the output in the trainer kit with truth table                              |

| 11 | Application Areas      | Integrated in the calculators and At Networking side the Full adder is used mostly. |

| 12 | Remarks                |                                                                                     |

| 13 | Faculty Signature with |                                                                                     |

|    | Date                   |                                                                                     |

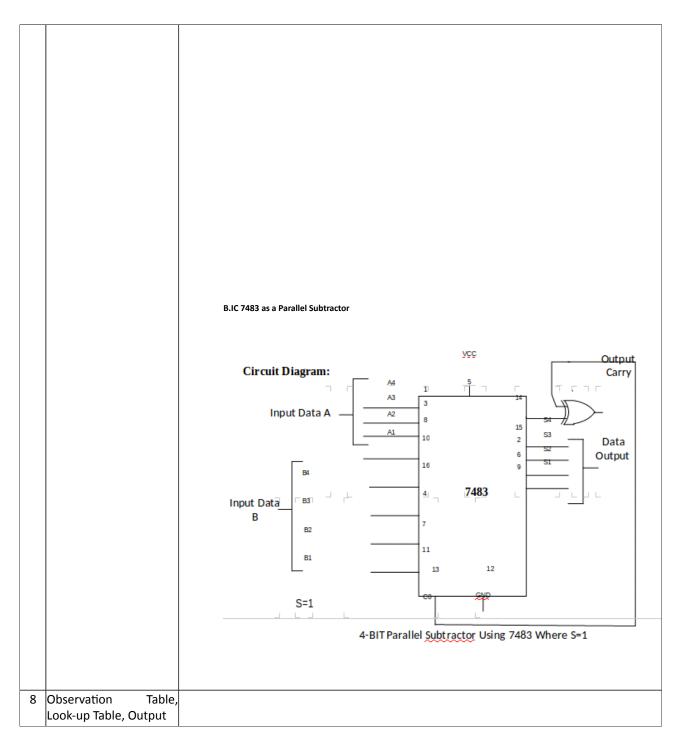

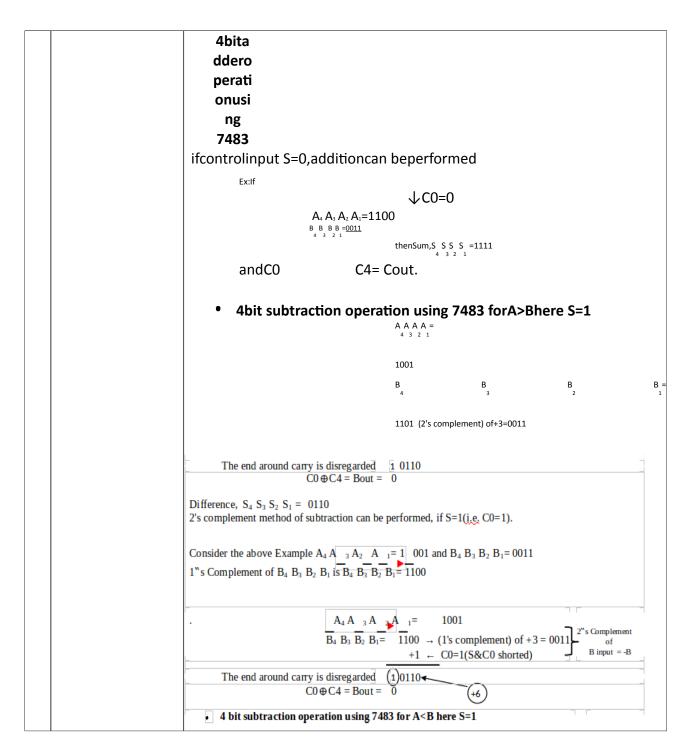

# Experiment 03 : <u>PARALLEL ADDER AND SUBTRACTOR USING 7483</u>

| -                                | Experiment No.:                        | 3 Marks                               | Date Planne                   | ł               | Date            |              |  |

|----------------------------------|----------------------------------------|---------------------------------------|-------------------------------|-----------------|-----------------|--------------|--|

|                                  |                                        |                                       |                               |                 | Conducted       |              |  |

| 1                                | Title                                  | PARALLELADDER ANDSUBTRACTOR USING7483 |                               |                 |                 |              |  |

| 2                                | Course Outcomes                        | Design the paralle                    | l adder & subtractor circuits | and compare b   | oth the circuit | S            |  |

| 3                                | Aim                                    | TorealizeParal                        | lel Adder and Subtracto       | or Circuits usi | ng IC 7483      |              |  |

| 4 Material / EquipmentLab Manual |                                        |                                       |                               |                 |                 |              |  |

|                                  | Required                               | IC 7483, IC 74                        | 86, etc.                      |                 |                 |              |  |

|                                  | Theory, Formula,<br>Principle, Concept |                                       |                               |                 |                 |              |  |

| 6                                | Activity, Algorithm,                   | 1.Connectones                         | etofinputsfromA1toA4          | oinsand the ot  | hersetfrom      | B1toB4,on    |  |

|                                  | Pseudo Code                            | the IC 7483.                          |                               |                 |                 |              |  |

|                                  |                                        | 2.Connectthep                         | ins fromS1 to S4 to out       | out terminals   |                 |              |  |

|                                  |                                        | 3.ShortS,C0toX<br>andobtainthe        | ORgate1inputandother          | inputtakefroi   | mC4             |              |  |

|                                  |                                        | OutputCarry Co                        | out (Output Borrow Bo         | ut).            |                 |              |  |

|                                  |                                        | 4.In ordertoPe                        | form Addition take S=0        |                 |                 |              |  |

|                                  |                                        | 5.Inordertoimp                        | lementtheIC7483asasu          | btractor,Take   | S=1,Applyth     | neBinput     |  |

|                                  |                                        | throughXOR ga                         | tes (essentially taking c     | omplement       | ofB).           |              |  |

|                                  |                                        | 6.Apply the inj                       | outs to theadder/ subt        | ractorcircuits  | as shown        | in the truth |  |

| (All all all all all all all all all all | SKIT      | Teaching Process  | Rev No.: 1.0    |

|------------------------------------------|-----------|-------------------|-----------------|

|                                          | Doc Code: | EC.SKIT.Ph5b1.F03 | Date:18-10-2019 |

|                                          | Title:    | Course Lab Manual | Page: 26 / 71   |

| 1 |

|---|

| 1 |

| 1 |

|   |

| SKIT      | Teaching Process  | Rev No.: 1.0    |

|-----------|-------------------|-----------------|

| Doc Code: | EC.SKIT.Ph5b1.F03 | Date:18-10-2019 |

| Title:    | Course Lab Manual | Page: 27 / 71   |

|   | 1  | an POL | ene . | -  |

|---|----|--------|-------|----|

| 1 | A  | 100    | -     | 51 |

| ( | 5  | 10     | 33    |    |

|   |    |        |       | 74 |

|   | ς. | -      |       |    |

|   | SKIT      | Teaching Process  | Rev No.: 1.0    |

|---|-----------|-------------------|-----------------|

| ) | Doc Code: | EC.SKIT.Ph5b1.F03 | Date:18-10-2019 |

|   | Title:    | Course Lab Manual | Page: 28 / 71   |

| Α     | .IC 74   | 483 a     | is a P     | Parall   | elAd      | der        |    |      |                 |            |           |           |  |

|-------|----------|-----------|------------|----------|-----------|------------|----|------|-----------------|------------|-----------|-----------|--|